- Cache paměti -

Cache paměti:

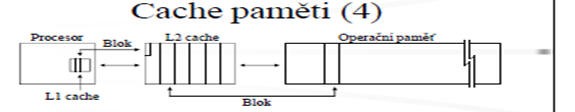

-rychlá vyrovnávací paměť mezi rychlý, zařízením (např.

procesorem) a pomalejším zařízením (např. operační pamětí).

-vyrobena z

obvodů SRAM s přístupovou dobou 1-20 ns

V dnešní počítačích se běžně

používají dva, popř. tři druhy cache pamětí.:

L2 (externí, sekundární) cache:

• Umístěna mezi pomalejší operační pamětí a rychlým procesorem.

• Slouží jako

vyrovnávací paměť u počítačů s výkoným procesorem, které by byly bez ní operační

paměti velmi zpomalovány.

• První L2 cache paměti se objevují u počítačů s

procesorem 80386 (o kapacitě 32kB, 64 kB)

• S výkonnějšími procesory se

postupně zvyšuje i kapacita (128 kB, 256 kB, 512 kB, 1024 kB a více)

• Řízena

řadičem cache paměti (součást čipové sady, popř. čipu procesoru)

• Osazení na

:

o Základní desce

o V pouzdře procesoru

o Na čipu

L1 (interní,

primární) cache:

• Slouží k vyrovnání rychlosti velmi výkonných procesorů a

pomalejších L2 cache pamětí

• Integrována přímo na čipu procesoru

• Poprvé

se objevuje u procesoru 80486 (s kapacitou 8kB)

• Řízení řadičem L1 cache

pamětí, která je integrován na čipu procesoru.

• Práce cache paměti vychází ze skutečnosti, že program má tendenci se při své

práci určitou dobu zdržovat na určitém místě paměti, a to jak při zpracování

instrukcí, tak při načtení (zapisování) dat z (do) paměti. Tzv. princip

lokality.

• Pokud dojde k zaplnění cache paměti a je potřeba zavést další

blok, je nutné, aby některé z bloků, cache paměť opustil.

• Nejčastěji se k

tomuto používá LRU (Least Recently Used) algoritmu, tj. algoritmu, který vyřadí

nejdéle nepoužívaný blok.

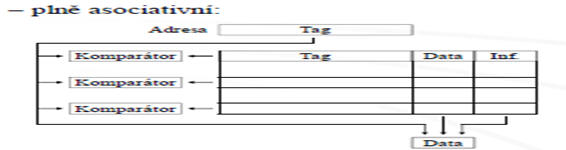

• Cache paměti neuchovává souvislý adresový prostor

bývají organizovány jako tzv. asociativní paměti.

• Asociativní paměti jsou

tvořeny tabulkou (tabulkami), které obsahuje:

o Tagy: klíče, podle kterých se

v asociativní paměti vyhledává.

o Uchovávané informace: data a instrukce

o

Další informace nutné k zajištění správné funkce paměti, např. informace:

O

platnosti (neplatnosti) uložených dat

Pro realizaci LRU algoritmu

Protokolu MESI (Modofied Exclusive Shared Invalid)

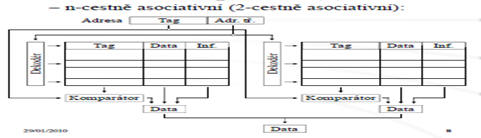

• Rozdělení cache pamětí

podle stupně asociativity:

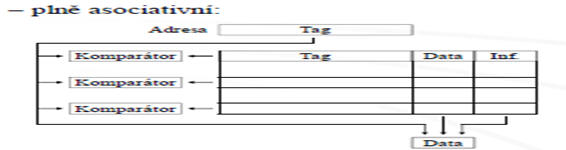

o Plně asociativní

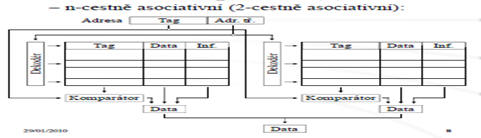

• N-cestně asociativní (2-cestně asociativní):

• Přímo mapované (1-cestně asociativní)

• Podle způsobu práce při zapisování dat lze cache paměti ještě rozdělit do dvou

skupin:

o Write.throught:

V případě zápisu procesoru do cache paměti

dochází okamžitě ik zápisu do operační paměti

o Write-back:

Data jsou

zapisována do operační paměti až ve chvíli, kdy je to třeba, a nikoliv okamžitě

při jejich změně.

K zápisu dat do operační paměti tedy dochází např. v

okamžiku, kdy je cache paměť zcela zaplněna a je třeba do ní umístit nová data

Tento způsob práce cache paměti vykazuje oproti předešlému způsobu vyšší výkon

• Kromě L1 a L2 cache pamětí je možné se sektak i se specializovanými cache

pamětmi umístěnými mezi operační paměť a některé pomalejší zařízení (pevný disk,

apod.).