- Operační paměti -

• Paměť: zařízení, které slouží k ukládání programů a dat, s nimiž počítač

pracuje

• Paměti počítače lze rozdělit do tří základních skupin:

o

Registry:

Paměťová místa na čipu procesoru

Jsou používány pro

krátkodobé uchování právě zpracovávaných informací

o Vnitřní (interní):

Paměti osazené většinou uvnitř základní jednotky

Realizovány pomocí

polovodičových součástek

Jsou do nich zaváděný právě spuštěné programy a

data, se kterými tyto programy pracují

o Vnější (externí):

Paměti

realizované většinou za pomoci zařízení používajících výměnná media v podobě

disků či magnetickém nebo optickém principu

Slouží pro dlouhodobé uchování

informací a zálohování dat

• Statičnost / dynamičnost:

o Statické paměti

Uchovají informaci po celou dobu, kdy je paměť připojena ke zdroji

elektrického napětí

o Dynamické paměti:

Zapsanou informaci mají tendenci

ztrácet i v době, kdy jsou připojeny k napájení

Informace v takových

pamětech je tedy nutné neustále periodicky oživovat, aby nedošlo k jejich

ztrátě.

• Destruktivnost

o Přečtená informace z paměti vede ke ztrátě této

informace. Aby zde opět mohla být musí být znovu nahrána

• Nedestruktivní při

čtení

o Přečtení této informace žádným negativním způsobem tuto informaci

neovlivní

• Přístup

o Sekvenční

Před zpřístupněním informace z

paměti je nutné přečíst všechny předcházející informace

o Přímý

Je možné

zpřístupnit přímo požadované informace

ROM – Read Only Memory

• Paměti

určené pouze pro čtení uložených informací

• Informace jsou do těchto pamětí

pevně zapsány při

• jejich výrobě.

• Potom již není možné žádným způsobem

jejich obsah změnit

• Jedná se o statické a energeticky nezávislé paměti

PROM – Programable Read Only Memory

• Neobsahují po vyrobení žádnou pevnou

informaci

• Příslušný zápis informace provádí uživatel

• Zápis je možné

provést pouze jednou a poté již paměť slouží stejně jako paměť ROM

• Zápis

informace se provádí vyšší hodnotou elektrického proudu (cca 10 mA), která

způsobí přepálení tavné pojistky

• Paměti PROM představují statické a

energeticky nezávislé paměti

EPROM – Eraseable PROM

• Statické energeticky

nezávislé paměti určené pro čtení i zápis informací

• Zapsané informace je

možné vymazat působením ultrafialového záření

• Realizovány pomocí

speciálních unipolárních

• tranzistorů, které jsou schopny na svém přechodu

• udržet elektrický náboj po dobu až několika let

EEPROM - Electrically EPROM

• Mají podobné chování jako paměti EPROM, tj. jedná se statické, energeticky

nezávislé paměti, které je možné naprogramovat a později z nich informace

vymazat

• Vymazání se provádí elektricky a nikoliv pomocí UV záření

•

Vyrábí se pomocí speciálních tranzistorů vyrobených technologií MNOS (Metal

Nitrid Oxide Semiconductor)

• Jedná se o tranzistory, na jejichž řídící

elektrodě (Gate) je nanesena vrstva nitridu křemíku (Si3N4) a pod ní je umístěna

tenká vrstva oxidu křemičitého (SiO2)

• Buňka paměti EEPROM pracuje na

principu tunelování (vkládání) elektrického náboje na přechod těchto dvou vrstev

Paměti Flash

• Obdoba pamětí EEPROM

• Paměti, které je možné naprogramovat

a které jsou statické a energeticky nezávislé

• Vymazání se provádí

elektrickou cestou, jejich přeprogramování je možné provést přímo v počítači

• Paměť typu flash tedy není nutné před vymazáním (naprogramováním) z počítače

vyjmout a umístit ji do speciálního programovacího zařízení

• Narozdíl od

EEPROM se u pamětí flash provádí mazání nikoliv po jednotlivých buňkách, ale po

celých blocích

• Paměťová buňka je tvořena tranzistorem, jeho elektroda gate

je rozdělena na dvě části:

o Control Gate:

připojená k adresovému vodiči

o Floating Gate:

oddělená od control gate izolační vrstvou

umožňuje

uložení elektrického náboje, pomocí něhož buňka

uchovává hodnotu logická 0

nebo logická 1

• Flash paměti se dělí do dvou základních skupin:

NOR

flash:

o poskytují rozhraní s vyhrazenými adresovými a datovými vodiči

umožňují přímý přístup k dané paměťové buňce

o chovají se jako paměti, které

jsou mapované do určité části adresového prostoru

o dovolují používat

techniku XIP –Execute In Place: je možné přímo

o spouštět programy, které

jsou v nich uložené

o spouštěné programy z těchto pamětí není nutné nejprve

kopírovat do paměti RAM

o mnohdy se však používá technika RAM shadowing, tj.

kód z paměti flash se nejdříve zkopíruje do rychlejší paměti RAM, kde je

následně spuštěn

NAND Flash:

• jsou připojeny pomocí relativně

jednoduchého rozhraní

• nevyžadují plnou šířku adresové a datové sběrnice

• data a příkazy jsou multiplexovány do 8 I/O linek, pomocí nichž jsou zasílány

do interního registru

• práce s flash pamětí NAND probíhá typicky v

následujících krocích:

o zaslání příkazu (např. read nebo write)

o zaslání

4bytové adresy vyjadřující, odkud budou data čtena, resp. Kam budou zapisována

o vyčkání, až flash paměť umístí požadovaná data do výstupního registru nebo

zaslání zapisovaných dat

o přečteni, resp. zapsání dat

o výhodou tohoto

řešení je, že není nutné měnit počet vývodů příslušných integrovaných obvodů s

měnící se kapacitou flash paměti snadnější upgrade

o ve srovnání s NOR

flash paměťmi jsou pomalejší při čtení, ale rychlejší při zápisu i při mazání

o dovolují cca 100000 – 1000000 smazání a zápisů

o používány zejména pro

výrobu paměťových karet (např. SD card, SmartMedia, CompactFlash, Memory Stick)

Paměti RAM

RAM - Random Access Memory

o Paměti určené pro zápis i pro

čtení dat

o Jedná se o paměti, které jsou energeticky závislé

o Podle

toho, zda jsou dynamické nebo statické, jsou dále

rozdělovány na:

o DRAM –

Dynamické RAM

o SRAM – Statické RAM

SRAM - Static Random Access Memory

o Uchovávají informaci v sobě uloženou po celou dobu, kdy jsou připojeny ke

zdroji elektrického napájení

o Paměťová buňka je realizována jako bistabilní

klopný obvod, tj. obvod, který se může nacházet vždy v jednom ze dvou stavů,

které určují, zda v paměti je uložena 1 nebo 0

o Mají nízkou přístupovou dobu

(1 – 20 ns)

o Jejich nevýhodou je naopak vyšší složitost a z toho plynoucí

vyšší výrobní náklady

o Jsou používány především pro realizaci pamětí typu

cache (L1, L2 i L3)

o Paměťová buňka používá dvou datových vodičů:

Data:

určený k zápisu do paměti

Data: určený ke čtení z paměti

Hodnota na

tomto vodiči je vždy opačná než hodnota uložená v paměti

DRAM - Dynamic

Random Access Memory

o Informace je uložena pomocí elektrického náboje na

kondenzátoru

o Tento náboj má však tendenci se vybíjet v době, kdy je paměť

připojena ke zdroji elektrického napájení

o Aby nedošlo k tomuto vybití a tím

i ke ztrátě uložené informace, je nutné periodicky provádět tzv. refresh, tj.

oživování paměťové buňky

o Buňka paměti DRAM je velmi jednoduchá a dovoluje

vysokou integraci a nízké výrobní náklady

o Díky těmto vlastnostem je

používána k výrobě operačních pamětí

o Její nevýhodou je však vyšší

přístupová doba (10 – 70 ns) způsobená nutností provádět refresh a časem

potřebným k nabití a vybití kondenzátoru

o Operační paměti mají ve srovnání s

jinými typy vnitřních pamětí podstatně vyšší kapacitu nutnost jiné konstrukce

o Paměti DRAM jsou konstruovány jako matice, v nichž se jedna paměťová buňka

zpřístupňuje pomocí dvou dekodérů

o Řadič operační paměti adresu rozdělí na

dvě části, z nichž každá je přivedena na vstup samostatnému dekodéru (jeden

dekodér vybere řádek a druhý sloupec)

o Protože paměťové obvody nemohou mít příliš velký počet vývodů, je nutné, aby

adresa řádku i sloupce byla předávána po stejné sběrnici

o Platnost adresy

řádku a sloupce na sběrnici je dána (potvrzována) signály:

RAS (Row Access

Strobe): adresa řádku

CAS (Coloumn Access Strobe): adresa sloupce

Paměti

FPM DRAM

• Adresa řádku je stejná po celou dobu, kdy se provádí přístup k

datům z tohoto řádku

• Paměti FPM DRAM umožňují přístup s burst časováním

5-3-3-3

Paměti EDO DRAM (Enhanced Data Output)

někdy uváděna jako Hyper

Page Mode DRAM.

• asynchronní paměť

• oproti FPM je EDO mírně rychlejší

(zhruba o 5%)

• přístupová doba 60 ns

• SIMM i DIMM modulů.

•

Specifikace:

o 168 / 72 pinů

o napájecí napětí: 3.3 nebo 5V

o kapacita:

až 32MB

• Data se stávají neplatnými, až v okamžiku, kdy signál CAS přechází

znovu do úrovně log. 0

• Paměti EDO DRAM umožňují přístup s burst časováním

5- 2-2-2

Paměti SDRAM (Synchronized Dynamic Random Access Memory)

•

synchronní paměť - pracuje synchronně podle externího taktu

• oproti EDO

pamětem poskytuje vyšší výkon. Rychlejší varianty následovaly krátce poté.

•

Specifikace:

o PC66 – PC133 , pracovní frekvence: 66 – 133 MHz

o

propustnost: 533 - 1066 MB/s

o 168 pinů

o napájecí napětí: 3.3 V

o

kapacita: ještě dnes běžně dostupná v kapacitách od 64 do 512 MB

• Pracují

synchronně s procesorem

• Jsou rozděleny do banků

• Umožňují přístup s

burst časováním 5-1-1-1

• Musí svou frekvencí odpovídat frekvenci systémové

sběrnice

• Vyráběny s frekvencemi:

• PC66: pro systémovou sběrnici s

taktem 66 MHz

• PC100: pro systémovou sběrnici s taktem 100 MHz

• PC133:

pro systémovou sběrnici s taktem 133 MHz

Paměti DDR SDRAM (Double Data Rate)

• 2000 (266MHz = DDR266)

• DDR400 (PC3200) JEDEC

• DDR600 overclocking -

vysoké napájecí napětí (i přes 3 V).

• nízkonapěťová verze DDR pamětí LPDDR,

1,8 – 1,9 V a vykazují až o 40% nižší spotřebu.

• Specifikace:

o DDR200 -

DDR400 , pracovní frekvence: 200 – 400 MHz efektivně

o propustnost: 1,6 - 3,2

GB/s

o 184 pinů

o napájecí napětí: 2.5 V (2.6 V pro DDR400)

o 2-bit

prefetch

o kapacita: 64 MB až 2 GB

Paměti DDR SDRAM

DDR SDRAM - Double

Data Rate SDRAM

• Rychlejší verze SDRAM, která při stejné frekvenci dosahuje

dvojnásobného výkonu

• Tohoto je dosaženo tím, že veškeré operace jsou

•

synchronizovány s náběžnou i sestupnou hranou hodinového signálu (CLK)

•

Provádí předvýběr dvou bitů, které ukládá do svých V/V bufferů

• Poznámka:

paměťové moduly SDRAM a DDR SDRAM jsou vzájemně nekompatibilní

Paměti DDR2

SDRAM

• nástupce DDR

• vyšší dosažitelné frekvence a vyšší propustnost

• nižší napájecí napětí, nižší spotřeba

• mírně horší časování oproti DDR

• Specifikace:

o DDR2-400 – DDR2-800

o pracovní frekvence: 400 – 800 MHz

efektivně

o propustnost: 3.2 – 6.4 GB/s

o 240 pinů

o napájecí napětí:

1.8 V (maximálně 1.9 V)

o 4-bit prefetch

o kapacita: 128 MB až 8 GB

•

Standard vycházející z pamětí DDR SDRAM

• Data jsou čtena (zapisována) s

nástupnou i sestupnou hranou hodinového signálu (podobně jako u DDR SDRAM)

•

Poskytují dvojnásobnou přenosovou rychlost oproti DDR SDRAM

• Paměti DDR2

SDRAM mají asi o 50% menší spotřebu elektrické energie Napájecí napětí je 1,8 V

(u DDR SDRAM je napájecí

• napětí 2,5 V)

• Dosažení vyšší přenosové

rychlosti je založeno na skutečnosti, že jádro paměťového obvodu (pracující na

frekvenci např. 100 MHz) může při každém čtecím cyklu předvybrat další 4 bity z

paměťové matice a uložit je V/V bufferů

• Adresa předvybíraných 4 bitů je

dána interní logikou paměťového obvodu

• Výsledkem je, že V/V část paměti

může pracovat dvojnásobnou frekvencí oproti jejímu jádru

• Následným použitím

nového komunikačního protokolu je umožněno provedení 4 transakcí během jednoho

taktu¨

• Poznámka: paměťové moduly DDR2

• SDRAM a DDR SDRAM nejsou

vzájemně kompatibilní

Paměti DDR3 SDRAM

• pracovní napětí 1,35V - 1.65 V

• 800 – 1600 MHz efektivně

• propustnost cca.12.8 GB/s

• snížení spotřeby

• vyšší latence

• Specifikace:

o DDR3-800 - DDR3-1600

o pracovní

frekvence 800 – 1600 MHz efektivně

o propustnost 6.4 GB/s – 12.8 GB/s

o

240 pinů

o napájecí napětí od pod 1.65 V

o 8-bit prefetch

o kapacita:

1GB a výše

• Nový standard vycházející z pamětí DDR2 SDRAM

• Data jsou

přenášena s nástupnou i sestupnou hranou hodinového signálu (jako u DDR a DDR2

SDRAM)

• Umožňují, aby jejich V/V sběrnice pracovala se čtyřnásobnou

rychlostí oproti paměťovým buňkám

• Poskytují vyšší (teoreticky dvojnásobnou)

přenosovou rychlost než DDR2 SDRAM

• Zvýšení přenosové rychlosti je dosaženo

předvýběrem 8 bitů při každém čtecím cyklu a jejich uložením do V/V bufferu

•

Napájecí napětí je 1,5 V

• Mají asi o 30% menší spotřebu elektrické energie

než paměti DDR2 SDRAM

• Poznámka:

o paměťové moduly DDR2 a DDR3 SDRAM

nejsou vzájemně kompatibilní

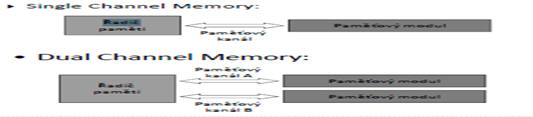

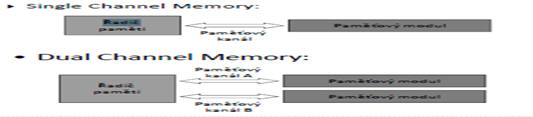

Dual Channel DDR

• Nejedná se o nový typ

paměti, ale o novou architekturu základních desek využívající paměti DDR, DDR2 a

DDR3 SDRAM

• Pro práci s pamětí se využívají dva kanály

• Data jsou

přenášena po 128 bitech (64 bitů pro každý kanál)

• Tímto se minimalizují

doby, kdy není možné k paměti přistupovat (memory latencies)

• Pro využití

architektury Dual Channel DDR je zapotřebí:

o oba moduly ve dvojici musí mít

stejné parametry

• Použití Dual Channel DDR teoreticky zdvojnásobuje

přenosovou rychlost paměti

Časování pamětí

• Udává počty taktů potřebné k různým operacím, které jsou

prováděny v průběhu přístupu k paměti

• Operace:

• tRCD: RAS to CAS Delay:

(Row (Column) Access Strobe)

• časová prodleva (počet taktů) od okamžiku, kdy

je vybrán (aktivován) řádek do doby, kdy je možné vybrat sloupec a potvrdit jej

signálem CAS

• při sekvenčním čtení (zápisu) nemá příliš velký dopad, protože

data jsou čtena (zapisována) na stejném řádku, který je stalé aktivní

tCL:

CAS Latency:

• počet taktů potřebný k získání informace z paměťové buňky

poté, kdy byl vybrán její sloupec

• uplatňuje se při každém přístupu k paměti

má největší vliv na rychlost paměti

• tRP: RAS Precharge Time:

• počet

taktů nutný pro ukončení přístupu k jednomu řádku paměti a pro zahájení přístupu

k řádku jinému

• ve spojení s tRCD udává počet taktů nezbytných k přechodu z

jednoho řádku paměti na řádek druhý, kde již může být

• vybrán požadovaný

sloupec

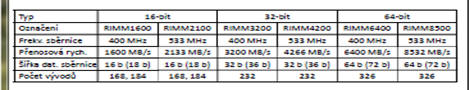

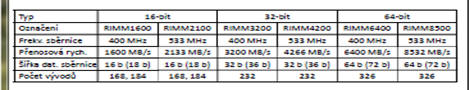

Paměti RDRAM (Direct Rambus DRAM)

• 1999 (Rambus, Intel)

•

obsahuje rychlou RDRAM sběrnici a řadič paměti

• oproti SDRAM navýšení

propustnosti ale vysoké latence

• 16 bit RIMMy, později 32 bit varianta - 10

GB/s

• vysoká cena

• vytlačeny DDR

• Specifikace:

o PC600 – PC1200

o pracovní frekvence: 300 - 600 MHz

o propustnost: 1200 – 2400 MB/s (v

případě dvou kanálů na modul a 242 pin verze až 4800 MB/s)

o 184 pinů

o

napájecí napětí: 1.8 V

o kapacita: 64 – 512 MB

• Technologie

(architektura) navržená firmou Rambus Inc.

• Poprvé použita u herní konzole

Nintendo 64

• Paměťové obvody jsou připojeny ke speciální vysokorychlostní

sběrnici, tzv. Rambus Channel

• Sběrnice pro paměti RDRAM pracuje synchronně

s danou frekvencí a data jsou přenášena s náběžnou i sestupnou hranou hodinového

signálu

Paměti RDRAM jsou (byly) vyráběny v následujících variantách:

•

Concurrent RDRAM:

o šířka datové části sběrnice je 8 bitů (9 bitů)

o šířka

interní datové sběrnice jednotlivých paměťových obvodů je 64 bitů

o sběrnice

pracuje s rychlostí 300 MHz, popř. 350 MHz

o přenosová rychlost je 600 MB/s

(700 MB/s)

o odpovídající paměťové moduly (RIMM) jsou označovány jako PC600 a

PC700

• Direct RDRAM:

o šířka datové části sběrnice je 16 bitů (18 bitů)

o šířka interní datové sběrnice jednotlivých paměťových obvodů je 128 bitů

o

sběrnice pracuje s rychlostí 400 MHz, popř. 533 MHz

o přenosová rychlost je

1,6 GB/s (2,13 GB/s)

o odpovídající paměťové moduly (RIMM) jsou označovány

jako RIMM1600, RIMM2100, RIMM3200, RIMM4200, RIMM6400 a RIMM8500

• Paměťový

obvod je rozdělen do 32 banků

• Ke každému banku náleží sdílené operační

zesilovače (split bank), které zesilují přečtenou (zapisovanou) informaci z (do)

celého řádku (64 x 128 bitů = 8192 bitů)

• I/O Gating pracuje jako obousměrný

multiplexor/demultiplexor, který:

o při čtení vybere požadovaných 128 bitů

o při zápisu sestaví 8192 bitů

• Při čtení je následně 128 bitů

multiplexováno a po 16 bitech opouští paměťový obvod

• Při zápisu se nejprve

16bitové sady demultiplexují, čímž se vytváří 128bitová sada, která je poté přes

Write Buffer a I/O Gating zapsána do paměti

• Technologie RDRAM využívá ke

své činnosti „klasickou“ paměťovou buňku DRAM, která pracuje s frekvencí 100 MHz

(133 MHz)

• Paměti RDRAM při své činnosti využívají i tzv. řídících registrů,

které jsou zapojeny do sériové smyčky (SIn/SOut)

• V těchto registrech se

uchovává např.:

o identifikace obvodu

o parametry týkající se časování

paměti

o konfigurace paměti

• Vzhledem k tomu, že řídící registry jsou

za-pojeny do série, tak je nezbytné, aby volné pozice pro paměťové moduly (RIMM)

byly osazeny speciálním průchozím modulem (C-RIMM), který zabezpečí uzavření

sériové smyčky

• Architektura RDRAM může využívat i více kanálů (max. 4) pro

přenos dat mezi řadičem a paměťovými moduly

Organizace pamětí v PC

Operační paměti jsou integrovány na miniaturních deskách plošného spoje:

30-pin SIMM (Single Inline Memory Module):

• používány u většiny počítačů s

procesory 80286, 80386SX, 80386 a některých 80486

• mají 30 vývodů a šířku

přenosu dat 8 bitů (bezparitní) nebo 9 bitů (paritní)

• vyráběny s kapacitami

256 kB, 1 MB a 4 MB

72-pin SIMM (PS/2 SIMM):

• používány u počítačů s

procesory 80486 a Pentium

• mají 72 vývodů a šířku přenosu dat 32 bitů

(bezparitní) nebo 36 bitů (paritní – pro každý byte jeden paritní bit)

•

vyráběny s kapacitami 4 MB, 8 MB, 16 MB, 32 MB

• DIMM (Dual Inline Memory

Module):

• dnes nejpoužívanějším typem paměťových modulů

• počet vývodů:

o 168 vývodů: FPM DRAM, EDO DRAM, SDRAM

o 184 vývodů: DDR SDRAM

o 240

vývodů: DDR2 SDRAM a DDR3 SDRAM

• vyrábějí se s kapacitami 16 MB, 32 MB, 64

MB, 128 MB, 512 MB, 1024 MB, 2048 MB a 4096 MB

• šířka přenosu dat je 64 bitů

• používají se u počítačů s procesory Intel Pentium a vyššími

DIMM (Dual

Inline Memory Module):

• dnes nejpoužívanějším typem paměťových modulů

•

počet vývodů:

o 168 vývodů: FPM DRAM, EDO DRAM, SDRAM

o 184 vývodů: DDR

SDRAM

o 240 vývodů: DDR2 SDRAM a DDR3 SDRAM

• vyrábějí se s kapacitami 16

MB, 32 MB, 64 MB, 128 MB, 512 MB, 1024 MB, 2048 MB a 4096 MB

• šířka přenosu

dat je 64 bitů

• používají se u počítačů s procesory Intel Pentium a vyššími

RIMM (Rambus Inline Memory Module):

• paměťový modul pro obvody typu RDRAM

• pro Concurrent RDRAM jsou vyráběny jako:

o PC600: moduly pro frekvenci 300

MHz („600 MHz“)

o PC700: moduly pro frekvenci 350 MHz („700 MHz“)

• pro

Direct RDRAM existují v následujících variantách:

• Fully Buffered DIMM (FB-DIMM)

• princip rychlého sériového rozhraní, které

spojuje veškeré moduly (na jednom paměťovém kanálu)

• každý modul má AMB čip

(Advanced Memory Buffer)

• řetězení modulů - až 8 modulů na kanál

• DDR

SDRAM Dual-channel přístup na max. 4 moduly

• prodloužení dosahu řadiče

paměti pomocí opakovače

• menší množství pinů pro obsluhu na řadič paměti

• možno použít více paměťových řadičů

• lze bez problémů použít vyšší

množství paměťových modulů

Registered memory (někdy taky uváděná jako

„buffered“)

• vybavena dalším čipem (registrem), které řídí jak je k

paměťovým modulům a bankům přistupováno

• K paměti není přistupováno přímo,

ale přes zmiňovaný registr, který řeší problémy se čtením i zápisem z

jednotlivých buňek (částí paměti) v případě velkokapacitních modulů

• jakési

zadržení o hodinový cyklus a „osvěžení“ řídících signálů – samotná paměť přijde

do styku až s výsledkem těchto operací.

• z hlediska paměťového řadiče je

přístup do paměti snažší, ačkoliv za cenu snížení výkonu běžná u serverových

základních desek

• registered paměti mají běžně 2 a více adresovatelných

oblastí (tak zvaný „memory rank“) s šířkou sběrnice pro DDR SDRAM 72 bitů (z

toho 64 bity jsou data a 8 bitů tvoří ECC kód).

ECC

• detekce a opravy

chyb (ECC, Error-Correcting Code)

• slouží ke kontrole integrity dat (nejen u

operační paměti) uložených v paměti

• schopnost opravit chybu jednoho bitu

(single bit error correction)

• chyba ve dvou bitech (double bit error

detection)

SPD (Serial Presence Detect)

• uloženy standardní informace

• pracovní napětí

• časování pro určitou pracovní frekvenci pamětí

• Díky

SPD se tak většina uživatelů nemusí o nastavení časování paměti vůbec starat,

protože nastavení dle výrobce zajistí právě informace uložené na SPD čipu.

•

optimální chod

Paměťové banky

• Nejmenší jednotka paměti, která může být

do počítače přidána, popř. z počítače odebrána

• Velikost jednoho banku je

závislá na šířce datové sběrnice procesoru

• Je nutné, aby šířka přenosu dat

modulů v jednom banku byla stejná jako šířka datové sběrnice procesoru